### LV8860V

# ON Semiconductor®

http://onsemi.com

## Fan Motor Driver Single-Phase Full-Wave Driver

#### Overview

**Bi-CMOS IC**

LV8860V is a driver IC used for single-phase fan motor. High-efficiency and low-noise are realized by reducing reactive power using Silent PWM.

The operating range of LV8860V is wide. LV8860V also corresponds to 24V. Therefore, it is optimal for office automation equipment and factory automation equipment.

#### **Functions**

- Single-phase full wave operation by Silent PWM drive.

- Speed is controllable by PWM input.

- Hall bias output pin.

- Integrated Quick Start Circuit.

- FG (rotation detection) / RD (lock detection) output pin (open drain output)

- Integrated current limiter circuit (limit at I<sub>O</sub>=450mA with Rf=0.5Ω connection, limit value is determined based on Rf.)

- Integrated lock protector circuit and automatic recovery circuit.

- Integrated thermal shut-down (TSD) circuit.

#### **Specifications**

#### **Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter                    | Symbol                 | Conditions             | Ratings     | Unit |

|------------------------------|------------------------|------------------------|-------------|------|

| Maximum supply voltage       | V <sub>CC</sub> max    |                        | 36          | V    |

| OUT pin output current       | I <sub>OUT</sub> max   |                        | 0.7         | Α    |

| Output withstand             | V <sub>OUT</sub> max   |                        | 36          | ٧    |

| RD/FG output pin withstand   | V <sub>RD/FG</sub> max |                        | 36          | ٧    |

| RD/FG output maximum current | I <sub>RD/FG</sub> max |                        | 10          | mA   |

| RGL output maximum current   | I <sub>RGL</sub> max   |                        | 5           | mA   |

| HB output maximum current    | I <sub>HB</sub> max    |                        | 10          | mA   |

| PWM input pin withstand      | V <sub>PWM</sub> max   |                        | 6           | ٧    |

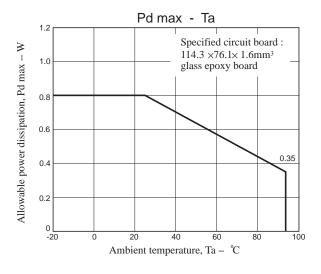

| Allowable power dissipation  | Pd max                 | * On a specified board | 0.8         | W    |

| Operating temperature        | Topr                   |                        | -40 to +95  | °C   |

| Storage temperature          | Tstg                   |                        | -55 to +150 | °C   |

<sup>\*</sup>Specified board: 114.3mm  $\times$  76.1mm  $\times$  1.6mm fiberglass epoxy printed circuit board

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### LV8860V

#### Recommended Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                                   | Symbol              | Conditions                          | Ratings         | Unit |

|---------------------------------------------|---------------------|-------------------------------------|-----------------|------|

| Operating supply voltage range              | V <sub>CC</sub> op1 | Recommended supply voltage range    | 7 to 34         | V    |

|                                             | V <sub>CC</sub> op2 | Boot guarantee supply voltage range | 6 to 34         | V    |

| Hall input common phase input voltage range | V <sub>ICM</sub>    |                                     | 0.3 to VRGL-2.0 | V    |

| SSW pin input voltage range                 | SSW                 |                                     | 1.0 to 3.0      | V    |

| Input PWM frequency range                   | PWMF                |                                     | 20 to 50        | kHz  |

#### **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 24$ V

| Danamatan                              | O. mak al         | Conditions                                          | Ratings              |                      |                      | 11.2 |  |

|----------------------------------------|-------------------|-----------------------------------------------------|----------------------|----------------------|----------------------|------|--|

| Parameter                              | Symbol            | Conditions                                          | min                  | typ                  | max                  | Unit |  |

| Circuit consumption current            | Icc               | Active                                              |                      | 2.2                  | 3.5                  | mA   |  |

|                                        | I <sub>CC</sub> o | Stand-by                                            |                      | 1.7                  | 2.7                  | mA   |  |

| RGL pin output voltage                 | VRGL              |                                                     | 4.7                  | 5.0                  | 5.3                  | V    |  |

| RGH pin output voltage                 | VRGH              |                                                     | V <sub>CC</sub> -4.3 | V <sub>CC</sub> -4.8 | V <sub>CC</sub> -5.3 | V    |  |

| HB pin output voltage                  | VHB               | IHB=5mA                                             | 1.16                 | 1.25                 | 1.28                 | V    |  |

| Output ON resistance                   | Ron               | I <sub>O</sub> =0.3A, upper and lower ON resistance |                      | 1.4                  | 2.0                  | Ω    |  |

| Hall input bias current                | IHIN              |                                                     |                      |                      | 1.0                  | μΑ   |  |

| Current limiter                        | VRF               |                                                     | 200                  | 225                  | 250                  | mV   |  |

| PWM pin input Low level                | VPWML             |                                                     | 0                    |                      | 1.0                  | V    |  |

| PWM pin input High level               | VPWMH             |                                                     | 2.5                  |                      | VRGL                 | V    |  |

| PWM input minimum pulse width          | TPWM              |                                                     |                      | 2                    |                      | μs   |  |

| RD/FG output pin Low voltage           | VRD/FG            | I <sub>RD/FG</sub> =3mA                             |                      | 0.22                 | 0.3                  | V    |  |

| FG output leakage current              | IRDL/FGL          | V <sub>RD/FG</sub> =24V                             |                      |                      | 10                   | μΑ   |  |

| FG comparator hysteresis width         | ΔVHYS             | including offset                                    | ±5                   | ±12                  | ±18                  | mV   |  |

| Output ON time in Lock-detection       | TACT              |                                                     | 0.74                 | 0.95                 | 1.16                 | sec  |  |

| Output OFF time in Lock-detection      | TDET              |                                                     | 7.0                  | 9.0                  | 11.0                 | sec  |  |

| Output ON/OFF ratio in Lock-detection  | TRTO              | TRTO=TDET/TACT                                      | 7.5                  | 9.0                  | 11.0                 |      |  |

| Thermal shutdown operating temperature | TSD               | * Design guarantee                                  |                      | 180                  |                      | °C   |  |

| Thermal shutdown hysteresis width      | ΔTSD              | * Design guarantee                                  |                      | 40                   |                      | °C   |  |

<sup>\*</sup> Design guarantee: Signifies target value in design. These parameters are not tested in an independent IC.

#### Truth table

| Operating state              | IN1 | IN2 | PWM | OUT1 | OUT2 | FG  | RD  |

|------------------------------|-----|-----|-----|------|------|-----|-----|

| Datation drive made          | Н   | L   |     | Н    | L    | L   | L   |

| Rotation – drive mode        | L   | Н   | Н   | L    | Н    | OFF | L   |

| 5                            | Н   | L   | L   | L    | اـ   | L   | لـ  |

| Rotation – regeneration mode | L   | Н   |     | L    | L    | OFF | L   |

| Stand-by mode                | -   | -   | L   | L    | OFF  | OFF | L   |

|                              | Н   | L   |     | OFF  | اـ   | L   | OFF |

| Lock protector               | L   | Н   | -   | L    | OFF  | OFF | OFF |

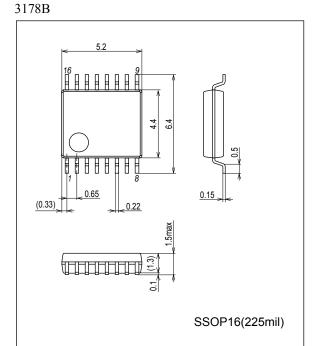

#### **Package Dimensions**

unit: mm (typ)

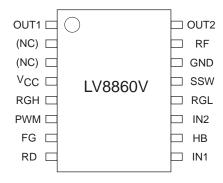

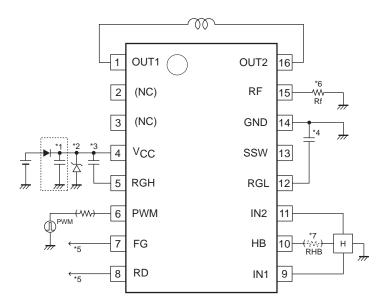

#### **Pin Assignment**

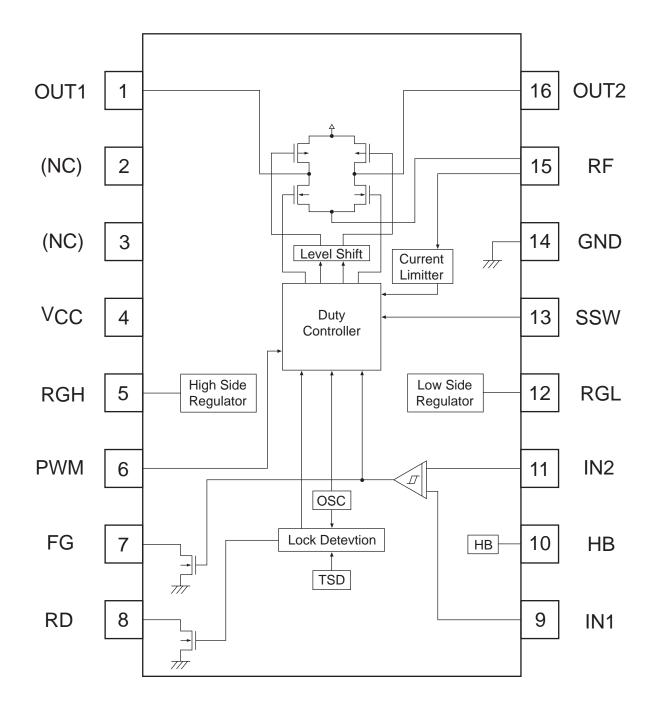

#### **Block Diagram**

#### **PIN** function

\*On circuit bord, ↑ means V<sub>CC</sub>, ↑ means RGL.

| NO. | Pin name        | Function                                                                                                                     | Equivalent circuit                      |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1   | OUT1            | Output pin for motor driver                                                                                                  |                                         |

|     |                 |                                                                                                                              |                                         |

| 16  | OUT2            |                                                                                                                              | 1) (16)                                 |

| 2   | NC              | No connect pin                                                                                                               |                                         |

| 3   | NC              | No connect pin                                                                                                               |                                         |

| 4   | V <sub>CC</sub> | Power supply pin                                                                                                             |                                         |

| 5   | RGH             | Regulator voltage output pin for the upper output Tr driver                                                                  | 5                                       |

| 6   | PWM             | Input pin for PWM control  * OPEN: pull up to High  * When input is High → output is High  When input is Low → output is Low | 6 W W W W W W W W W W W W W W W W W W W |

| 7   | FG              | FG (rotation detection) pulse output pin                                                                                     |                                         |

| 8   | RD              | RD (lock detection) signal output pin  * During rotation → output is Low  During lock → output is High                       | 8 1 1                                   |

| 9   | IN1             | Hall input + pin                                                                                                             |                                         |

| 11  | IN2             | Hall input - pin                                                                                                             | (1)<br>(1)                              |

| 10  | НВ              | Hall bias output pin                                                                                                         | Continued on payt page                  |

Continued on next page.

Continued from preceding page.

| NO. | Pin name | Function                                                                                                                                                                      | Equivalent circuit  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 12  | RGL      | Regulator voltage output pin for internal circuit and lower output Tr driver                                                                                                  | 12                  |

| 13  | SSW      | Voltage input pin for control between soft switches  * OPEN: pin voltage is 2V  * Soft switch zone is changed by connecting a resistance to RGL or GND to adjust pin voltage. | 90kΩ 13<br>800kΩ 13 |

| 14  | GND      | Ground pin                                                                                                                                                                    |                     |

| 15  | RF       | Resistive connection pin for current limiter                                                                                                                                  | 15                  |

#### **Sample Application Circuit**

- \*1 When diode Di is used to prevent destruction of IC from reverse connection, make sure to implement capacitor Cr to secure regenerative current route.

- \*2 If kickback at a phase change is greater, insert zener diode between GND and V<sub>CC</sub> or implement the larger capacitor between GND and V<sub>CC</sub> mentioned in \*1

- \*3 Make sure to implement enough capacitance  $0.1\mu F$  or greater between RGH pin and  $V_{CC}$  pin for stable performance.

- \*4 Make sure to implement enough capacitance 0.1μF or greater between RGL pin and GND pin for stable performance.

- \*5 FG pin and RD pin are open drain output. Keep the pins open when unused.

- \*6 The current limiter is activated when the current detection resistor voltage exceeds 225mV between RF and GND. Where Rf=0.5Ω, current limiter is activated at I<sub>O</sub>=450mA. Setting is made using Rf resistance.

- \*7 Hall element outputs stable hall signal with good temperature characteristic when it is biased with constant voltage from HB pin. If you wish to alleviate heating of IC, do not use HB pin. When you do not use this Pin (Pin HB), pull down with resistor of around 10kΩ (recommended).

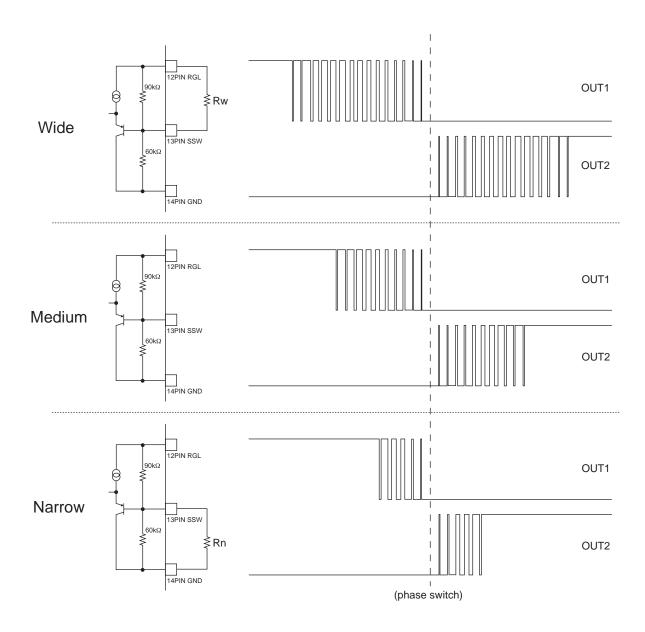

#### Adjustment of a direction between soft switches

LV8860V realizes high efficiency and low noise by controlling reactive power using soft switch before and after phase switch by variable PWM-duty.

The width of soft switch before and after switching is controlled by SSW pin voltage. Therefore, it is adjustable by connecting an external resistance to SSW. Adjustment voltage range is between 1V and 3V.

- \* Without adjustment (SSW is open \* this is a reference width of soft switch) ... with IC's internal resistance:  $VSSW = 5 \times 60k / (90k + 60k) = 2V$

- \* To widen width of soft switch (connect Rw (resistance) between RGL and SSW.)

...

$$VSSW = 5 \times 60k / (60k + 1 / (1/Rw + 1/90k))$$

ex.) Connect Rw =

$$75k\Omega$$

VSSW =  $5 \times 60k / (60k + 1 / (1/75k + 1/90k)) = 2.97V$

\* To narrow soft switch width (connect Rn (resistance) between SSW and GND.)

...

$$VSSW = 5 \times ((1/(1/Rn + 1/60k))/(90k + 1/(1/Rn + 1/60k)))$$

ex.) Connect  $Rn = 39k\Omega$

$$VSSW = 5 \times ((1/(1/39k + 1/60k)) / (90k + 1 / (1/39k + 1/60k))) = 1.04V$$

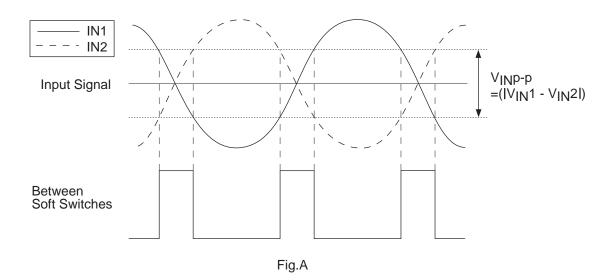

#### Setting value of input signal amplitude

The width of soft switch in LV8860V is controlled by input signal, IN1/IN2. The difference of input voltage (V<sub>INP</sub>-p) that creates width of soft switch is adjustable by SSW voltage (VSSW) of an external pin. The range of SSW input voltage is between 1V and 3V.

Difference of input signal amplitude in VSSW range:

- When VSSW = 1V (min), V<sub>INP</sub>-p = 30mV → make sure to input Hall signal with amplitude difference greater than 30mV.

- When VSSW = 2V (open), V<sub>INP</sub>-p = 90mV → make sure to input Hall signal with amplitude difference greater than 90mV.

- When VSSW = 3V (max), V<sub>INP</sub>-p = 150mV → make sure to input Hall signal with amplitude difference greater than 150mV.

- \* When input signal amplitude is greater than V<sub>INP</sub>-p (as shown in Fig. A below). Width of soft switch is defined as shown in Fig. A

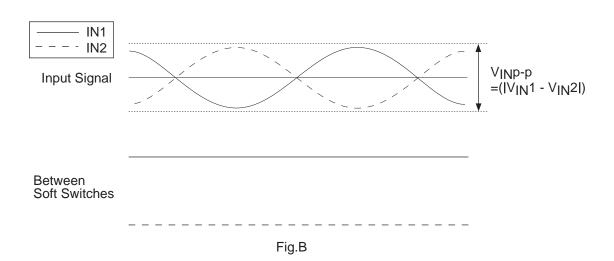

- \* When input signal amplitude is less than V<sub>INP</sub>-p (as shown in Fig. B below).

Since input signal is within the range of V<sub>INP</sub>-p in all rotations, the entire zone is the soft switch zone. Consequently, IC does not operate properly.

For such reason, make sure to input Hall signal with enough amplitude difference to SSW setting value so that IC operates properly.

#### **Description of operation**

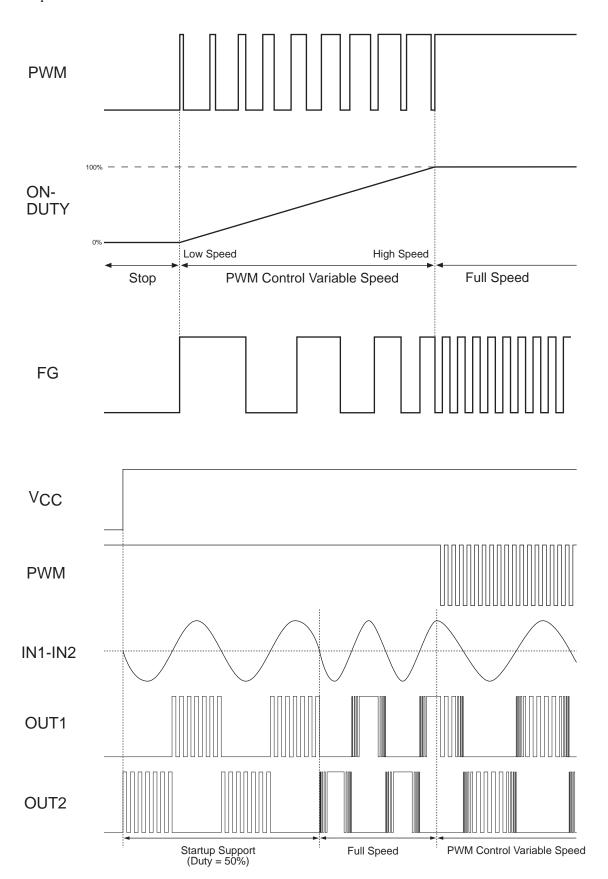

• PWM speed control waveform

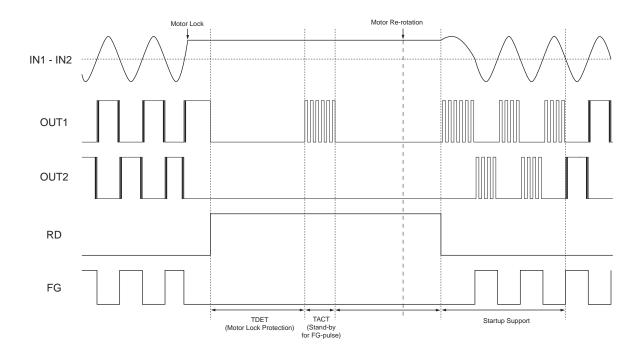

#### • Lock protection operation waveform

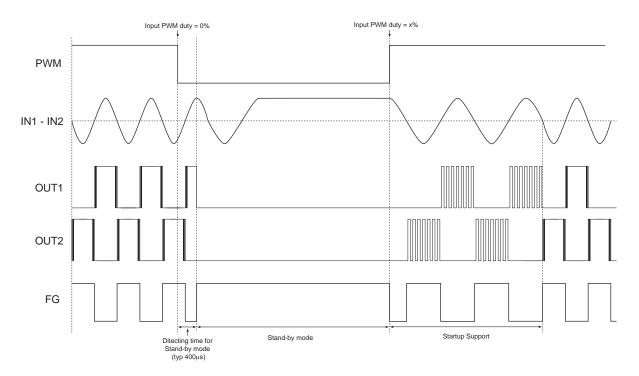

#### • Stand-by mode operation waveform

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa